# SPWF01SA SPWF01SC

**TBD**

## Datasheet - preliminary data

SPWF01SA

SPWF01SC

- Multiple antenna options available: integrated antenna or integrated u.FL connector

- Industrial operating temperature range

- FCC/CE/IC certified

- RoHS compliant

- · Surface mount PCB module

## **Applications**

- Smart appliances

- Industrial control and data acquisition

- Home automation & home energy

- Home security systems

- Wireless sensors

- Cable replacement

- Medical equipments

### **Features**

- Integrated 2.4 GHz IEEE 802.11 b/g/n transceiver

- Integrated STM32 ARM Cortex-M3

- Integrated 1.5 MB flash memory

- Integrated 64 KB RAM memory

- Integrated 32kHz XTAL to support low power modes

- 16 GPIOs, JTAG and serial port (UART, SPI, I2C) interfaces available

- Small form factor: 26.92 x 15.24 x 2.35 mm

- Up to +18 dBm output power

- Single voltage supply (3.3 V typ)

## **Description**

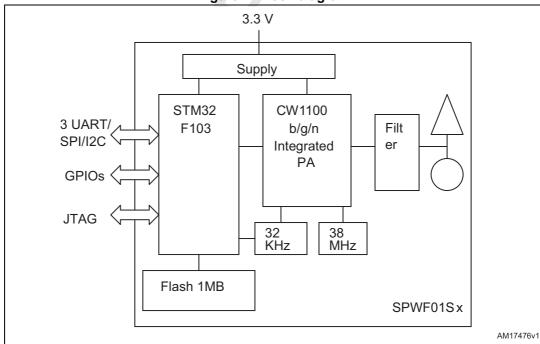

The SPWF01SA and the SPWF01SC intelligent Wi-Fi modules represent a plug and play and standalone 802.11 b/g/n solution for an easy integration of wireless Internet connectivity features into existing or new products.

Configured around a single-chip 802.11 transceiver with integrated PA and an STM32 32-bit microcontroller with extensive GPIO suite, the modules also incorporate timing clocks and voltage regulators.

The module is available either configured with an embedded micro 2.45 GHz ISM band antenna (SPWF01SA), or with an u.FL connector for external antenna connection (SPWF01SC).

With low power consumption and small form factor, the modules are ideal for fixed and mobile wireless applications, as well as challenging battery operated applications.

The SPWF01SA.11 and SPWF01SC.11 orderable parts are released with an integrated full featured TCP/IP protocol stack with added web server and additional application services capabilities. The SW package also includes an AT command layer interface for a friendly access to the stack functionalities via the UART serial port.

Figure 1. Block diagram

# 1 General electrical specifications

# 1.1 Typical results are at room temperature only

Table 1. Absolute maximum ratings

| Parameter                | Test condition/comment | Min. | Тур. | Max. | Unit |

|--------------------------|------------------------|------|------|------|------|

| 3.3 V supply             |                        | -0.3 |      | 4.0  | V    |

| Vin for 5V tolerant pins |                        | -0.3 |      | 5.5  | V    |

| Vin for all other pins   |                        | -0.3 |      | 2.8  | V    |

Table 2. Operating conditions and input power specifications

| Parameter                   |                         | Test condition/comment                                                 | Min. | Тур. | Max. | Unit |

|-----------------------------|-------------------------|------------------------------------------------------------------------|------|------|------|------|

| Operating temperature range |                         | Industrial                                                             | -40  |      | 85   | °C   |

| Input supply voltage        |                         | 3.3V Supply input                                                      | 3.1  | 3.3  | 3.6  | V    |

| Power s current             | Power save mode current | 100mS beacon period, 75 byte beacons @ 1Mbps, short Preamble, DTIM = 3 |      | 20   |      | mA   |

| 3.3 V                       | Sleep current           | 3.3V 25°C, no data retention, wakeup on events                         |      | 200  |      | μΑ   |

| supply                      |                         | DTIM 1, All beacons Received, no active data (average value)           |      | 900  |      | μΑ   |

|                             | TX current              | Peak, transmitting packets, 3.3V, 25°C                                 |      | 330  |      | mA   |

|                             | RX current              | Peak, Receiving packets 3.3V, 25°C                                     |      | 125  |      | mA   |

# 2 Digital interface specifications

Table 3. Digital Interface Specifications, I/O pins

| Parameter                |     | Test condition/comment | Min. | Тур. | Max. | Unit |

|--------------------------|-----|------------------------|------|------|------|------|

| lanuta                   | VIH |                        | 1.4  |      |      | V    |

| Inputs                   | VIL |                        | 0.6  |      |      | V    |

| Outputs                  | VOH | IOH=4mA                | 1.8  |      |      | V    |

|                          | VOL | IOL=4mA                |      |      | 0.4  | V    |

| Programmable             |     |                        | 80   |      | 120  | kΩ   |

| Pull up or down resistor |     |                        |      |      |      |      |

# 3 RF characteristics

Table 4.

| Parameter                        |                    | Test condition/comment                  | Min.                   | Тур.  | Max. | Unit |

|----------------------------------|--------------------|-----------------------------------------|------------------------|-------|------|------|

|                                  | 11b, 1 Mbps        |                                         |                        | -96   |      | dBm  |

|                                  | 11b, 2 Mbps        |                                         |                        | -93   |      | dBm  |

|                                  | 11b, 5.5 Mbps      |                                         |                        | -91   |      | dBm  |

|                                  | 11b, 11 Mbps       |                                         |                        | -87   |      | dBm  |

|                                  | 11g, 9 Mbps        |                                         |                        | -89.5 |      | dBm  |

|                                  | 11g, 18 Mbps       |                                         |                        | -86   |      | dBm  |

| RX Sensitivity <sup>(1)</sup>    | 11g, 36 Mbps       |                                         |                        | -80   |      | dBm  |

|                                  | 11g, 54 Mbps       |                                         |                        | -74.5 |      | dBm  |

|                                  | 11n, MCS1, 13 Mbps |                                         |                        | -86.5 |      | dBm  |

|                                  | 11n, MCS3, 26 Mbps |                                         |                        | -81.5 |      | dBm  |

|                                  | 11n, MCS5, 52 Mbps |                                         |                        | -74   |      | dBm  |

|                                  | 11n, MCS7, 65 Mbps |                                         |                        | -71   |      | dBm  |

| Channel to channel desensitivity | CH1 to 14          | 11g, 54 Mbps, 10%PER                    |                        | 1     |      | dB   |

| Maximum input signal             | CH7                | 11g, 54 Mbps                            |                        | -20   |      | dBm  |

|                                  | 11Mbps             |                                         |                        | 38    |      | dBc  |

|                                  | 9 Mbps             |                                         |                        | 20    |      | dBc  |

| Adjacent channel rejection       | 54 Mbps            |                                         |                        | 4     |      | dBc  |

|                                  | MCS1               |                                         |                        | 24    |      | dBc  |

|                                  | MCS7               |                                         |                        | 3     |      | dBc  |

|                                  | 11b, 1 Mbps        | @000 445                                |                        | 18.3  |      | dBm  |

|                                  | 11b, 11 Mbps       | — @802.11b spectral mask                | @802.11b spectral mask |       |      | dBm  |

| TV Output name (1)               | 11g, 9 Mbps        | @802.11g spectral mask                  |                        | 18.3  |      | dBm  |

| TX Output power (1)              | 11g, 54Mbps        | EVM=-27dB, 4.5%                         |                        | 13.7  |      | dBm  |

|                                  | 11n, MCS1          | @802.11n spectral mask                  |                        | 18.3  |      | dBm  |

|                                  | 11n, MCS7          | EVM=-27 dB                              |                        | 13.5  |      | dBm  |

| On board antenna gain            |                    | Average                                 |                        | -1.2  |      | dBi  |

| External antenna gain            |                    | SG901-1066 average including cable loss |                        | 2.8   |      | dBi  |

<sup>1.</sup> Output power and sensitivities are measured with a 50  $\Omega$  connection at the antenna port.

# 4 Pin out description

Table 5. Pin out

|               | Table 3. Fill Out                     |                                                                |                                                                |  |  |  |  |  |

|---------------|---------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|

| Signal name   | Pin number                            | Description/alternate function                                 | Notes                                                          |  |  |  |  |  |

|               | GPIO Pins and alternate SPI functions |                                                                |                                                                |  |  |  |  |  |

| GPIO0_MISO    | 16                                    | Alternate SPI MISO pin. Pull high on powerup to reset settings | Input pull down and 5 V tolerant                               |  |  |  |  |  |

| GPIO1_MOS1    | 17                                    | Alternate SPI MOSI                                             | Input pull down and 5 V tolerant                               |  |  |  |  |  |

| GPIO2_SPICS   | 19                                    | Alternate SPI chip select                                      | Floating and 5 V tolerant                                      |  |  |  |  |  |

| GPIO3_SCLK    | 1                                     | Alternate SPI clock                                            | Input pull down and 5 V tolerant                               |  |  |  |  |  |

| GPIO6_ADC0    | 22                                    | Wake up/sleep inhibit                                          | Input pull down and 5 V tolerant                               |  |  |  |  |  |

|               |                                       | Reserved Pins for future use                                   |                                                                |  |  |  |  |  |

| GPIO4_RXD3    | 18                                    | Alternate UART3 receive data input                             |                                                                |  |  |  |  |  |

| GPIO5_TXD3    | 20                                    | Alternate UART3 transmit data output                           |                                                                |  |  |  |  |  |

| GPIO7_ADC1    | 13                                    |                                                                |                                                                |  |  |  |  |  |

| GPIO8_ADC2    | 4                                     | Alternate UART2 transmit data output                           |                                                                |  |  |  |  |  |

| GPIO9_ADC3    | 7                                     | Alternate UART2 receive data input                             |                                                                |  |  |  |  |  |

|               |                                       | I2C Pins                                                       |                                                                |  |  |  |  |  |

| GPIO11_SCL    | 11                                    |                                                                |                                                                |  |  |  |  |  |

| GPIO12_SDA 12 |                                       |                                                                |                                                                |  |  |  |  |  |

| GPIO15_DAC    | 21                                    |                                                                |                                                                |  |  |  |  |  |

|               | Mon                                   | itoring purpose with no alternate fu                           | unction                                                        |  |  |  |  |  |

| GPIO10        | 5                                     | LED drive, blinking while run                                  |                                                                |  |  |  |  |  |

| GPIO13        | 15                                    | LED drive, wifi link                                           |                                                                |  |  |  |  |  |

| GPIO14        | 14                                    | LED drive, power up                                            |                                                                |  |  |  |  |  |

|               |                                       | <b>UART Pins</b>                                               |                                                                |  |  |  |  |  |

| RXD1          | 8                                     | UART1 receive data input                                       | 5 V tolerant                                                   |  |  |  |  |  |

| TXD1          | 6                                     | UART1 transmit data output                                     | 5 V tolerant                                                   |  |  |  |  |  |

| CTS1_DN       | 9                                     | UART1 clear to send input                                      | Active low, 5 V tolerant                                       |  |  |  |  |  |

| RTS1_DP       | 10                                    | UART1 request to send output                                   | Active low, 5 V tolerant                                       |  |  |  |  |  |

|               |                                       | Reset                                                          |                                                                |  |  |  |  |  |

| RESETn 3      |                                       | Reset input                                                    | Active low for 5 ms with pull up to 2.5 V DC. Not 5 V tolerant |  |  |  |  |  |

|               |                                       | JTAG test pins (1)                                             |                                                                |  |  |  |  |  |

| TRST_MISO3    | 28                                    | JTAG TRST_N, Used for 1M Flash                                 | 5 V tolerant                                                   |  |  |  |  |  |

|               |                                       |                                                                |                                                                |  |  |  |  |  |

Table 5. Pin out (continued)

| Signal name   | Pin number               | Description/alternate function  | Notes                                                               |  |  |  |

|---------------|--------------------------|---------------------------------|---------------------------------------------------------------------|--|--|--|

| TDI           | 27                       | JTAG TDI                        | 5 V tolerant                                                        |  |  |  |

| TMS           | 26                       | JTAG TMS                        | 5 V tolerant                                                        |  |  |  |

| TCK           | 29                       | JTAG TCK                        | 5 V tolerant                                                        |  |  |  |

| TDO_SCK3      | 30                       | JTAG TDO, Used for 1M Flash     | 5 V tolerant                                                        |  |  |  |

|               | Supply pins and paddle   |                                 |                                                                     |  |  |  |

| 3.3 V         | 24                       | Voltage supply                  | Decouple with 10 uF capacitor                                       |  |  |  |

| Ground        | 23                       | Ground                          |                                                                     |  |  |  |

| Ground Paddle | 25                       | Ground                          | Add plenty of ground vias for thermal dissipation and ground return |  |  |  |

|               | Firmware load pin access |                                 |                                                                     |  |  |  |

| воото         | 2                        | (See firmware load description) |                                                                     |  |  |  |

To enable the firmware download, Pin BOOT0 needs to be high during power up. RESETn need to be pulled low at least 5 ms to initiate the firmware download sequence.

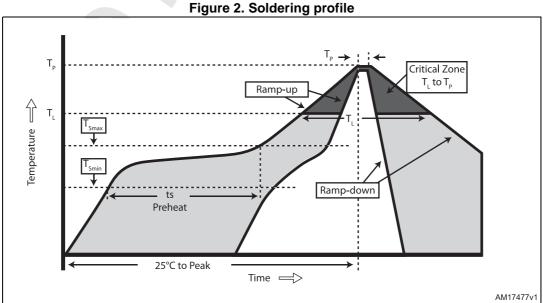

#### 5 Module reflow

The SPWF01SA and SPWF01SC are surface mount modules with a 6-layer PCB. The final assembly recommended reflow profiles are indicated here below.

The soldering phase must be executed with care: in order to avoid undesired melting phenomenon, particular attention must be paid to the setup of the peak temperature.

The following are some suggestions for the temperature profile based on IPC/JEDEC J-STD-020C, July 2004 recommendations.

Table 6. Soldering values

| Profile feature                                                                                                                                       | PB-free assembly               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Average ramp-up rate (T <sub>SMAX</sub> to T <sub>P</sub> )                                                                                           | 3 °C/sec max                   |

| Preheat:  - Temperature min. (T <sub>s</sub> min.)  - Temperature max. (T <sub>s</sub> max.)  - Time (T <sub>s</sub> min. to T <sub>s</sub> max) (ts) | 150 °C<br>200 °C<br>60-100 sec |

| Critical zone: Temperature T <sub>L</sub> Time T <sub>L</sub>                                                                                         | 217 °C<br>60-70 sec            |

| Peak temperature (T <sub>P</sub> )                                                                                                                    | 240 + 0 °C                     |

| Time within 5 °C of actual peak temperature (T <sub>P</sub> )                                                                                         | 10-20 sec                      |

| Ramp-down rate                                                                                                                                        | 6 °C/sec                       |

| Time from 25 °C to peak temperature                                                                                                                   | 8 minutes max.                 |

## 6 Regulatory compliance

## RF compliance

The RF certifications in Table 7 have been obtained.

Table 7. RF certification summary

|        |                 | Comment                                                         |

|--------|-----------------|-----------------------------------------------------------------|

| FCC ID | VRA-SG9011203   | On board antenna and external SG901-1066 with connector version |

| IC ID  | 7420A-SG9011203 | On board antenna and external SG901-1066 with connector version |

| ETSI   | Compliant       | Approved with on board antenna and connector version            |

Note: Sagrad SG901-1066 is the only approved antenna using the UFL connector version.

### FCC and IC

This module has been tested and found to comply with the FCC part 15 and IC RSS-210 rules. These limits are designed to provide reasonable protection against harmful interference in approved installations. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications.

However, there is no guarantee that interference may not occur in a particular installation.

This device complies with part 15 of the FCC rules. Operation is subject to the following two conditions:

This device may not cause harmful interference

and

2. this device must accept any interference received, including interference that may cause undesired operation.

Modifications or changes to this equipment not expressly approved by the part responsible for compliance may render void the user's authority to operate this equipment.

#### Modular approval, FCC and IC

FCC ID: VRA-SG9011203

IC: 7420A-SG9011203

In accordance with FCC part 15, the modules SPWF01SA and SPWF01SC are listed above as a modular transmitter device.

## **Label instructions**

When integrating the SPWF01SA and SPWF01Sc into the final product, it must be ensured that the FCC labelling requirements, as specified below, are satisfied. Based on the Public Notice from FCC, the product into which the ST transmitter module is installed must display a label referring to the enclosed module. The label should use wording such as the following:

Contains Transmitter Module

FCC ID: VRA-SG90112013

IC: 7420A-SG9011203

Any similar wording that expresses the same meaning may be used.

## CE

## CE Expert opinion: xxxxxxxxxxx

- Measurements have been performed in accordance with (report available on request):

- EN 300 328 V 1.7.1 (2006-10) (a)

- EN 301 489-17 V 2.1.1 (2009) (b)

- EN60950-1:2006 +A11:2009+A1:2010 (c)

Figure 3. CE certified

Figure 4. Top view of the module shield

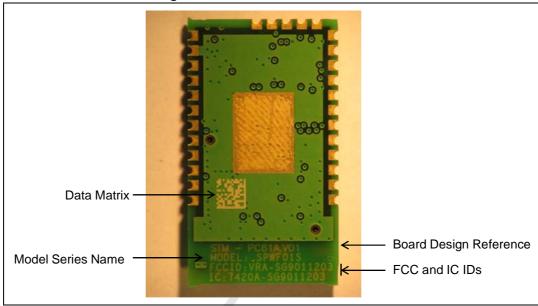

Figure 5. Bottom view of the module

#### Package mechanical data 7

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

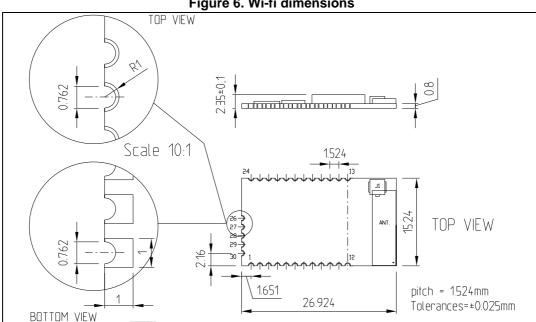

Figure 6. Wi-fi dimensions

Note:

An antenna area of 217X520 mils need to be free of any ground metallization or traces under the unit. The area extending away from the antenna should be free from metal on the PCB and housing to meet expected performance. Pin 25 is the required paddle ground and is not shown in this diagram.

1.524

24

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

1.524

Figure 7. Wi-fi footprint

PCB design requires detailed review of center exposed pad. This pad requires good thermal conductivity. Soldering coverage should be maximized and checked via x-ray for proper design. There is a trade off in providing enough soldering for conductivity and too much which allows the module to "float" on the paddle creating reliability issues. Sagrad recommends two approaches, a large center via that allows excess soldering to flow down into the host PCB with smaller vias arount it. Or many smaller vias with just enough space for the viscosity of the chosen solder/flux to allow some solder to flow into the smaller vias.

Each of these approaches need to result in 60% or more full contact solder coverage on the paddle after reflow. Sagrad strongly encourages PCB layout teams to work with their EMS providers to ensure vias and solder paste designs will result in satisfactory performance.

Note: Pin 1 is on the top left corner of this diagram. See note on the top view pin out for antenna to PCB interference requirements for the layout.

# 8 Ordering information

**Table 8. Ordering information**

| Order codes | Description                                                    |

|-------------|----------------------------------------------------------------|

| SPWF01SA.11 | Wifi module with integrated antenna and WiFi full stack        |

| SPWF01SC.11 | Wifi module with integrated u.FL connector and WiFi full stack |

Note:

Refer to the user guide for a complete list of features and commands available in the WiFi full stack.

# 9 Revision history

Table 9. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 30-May-2013 | 1a       | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Rev 1

16/16